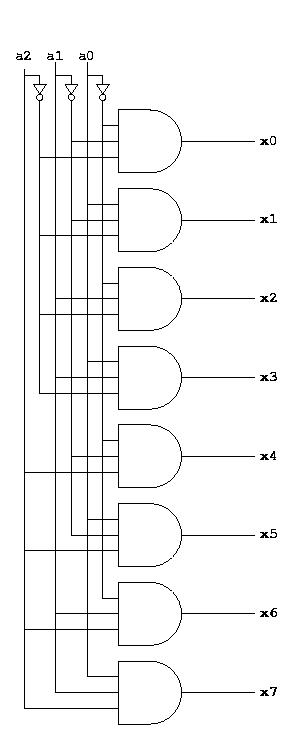

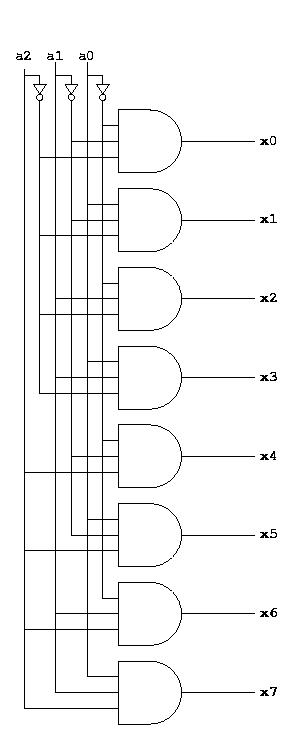

It is sometimes advantageous to separate this function from the rest of the circuit, since it is useful in many other applications. Thus, we obtain a new combinatorial circuit that we call the decoder. It has the following truth table (for n = 3):

a2 a1 a0 | d7 d6 d5 d4 d3 d2 d1 d0 ---------------------------------- 0 0 0 | 0 0 0 0 0 0 0 1 0 0 1 | 0 0 0 0 0 0 1 0 0 1 0 | 0 0 0 0 0 1 0 0 0 1 1 | 0 0 0 0 1 0 0 0 1 0 0 | 0 0 0 1 0 0 0 0 1 0 1 | 0 0 1 0 0 0 0 0 1 1 0 | 0 1 0 0 0 0 0 0 1 1 1 | 1 0 0 0 0 0 0 0Here is the circuit diagram for the decoder: