Architecture en pipeline : schémas

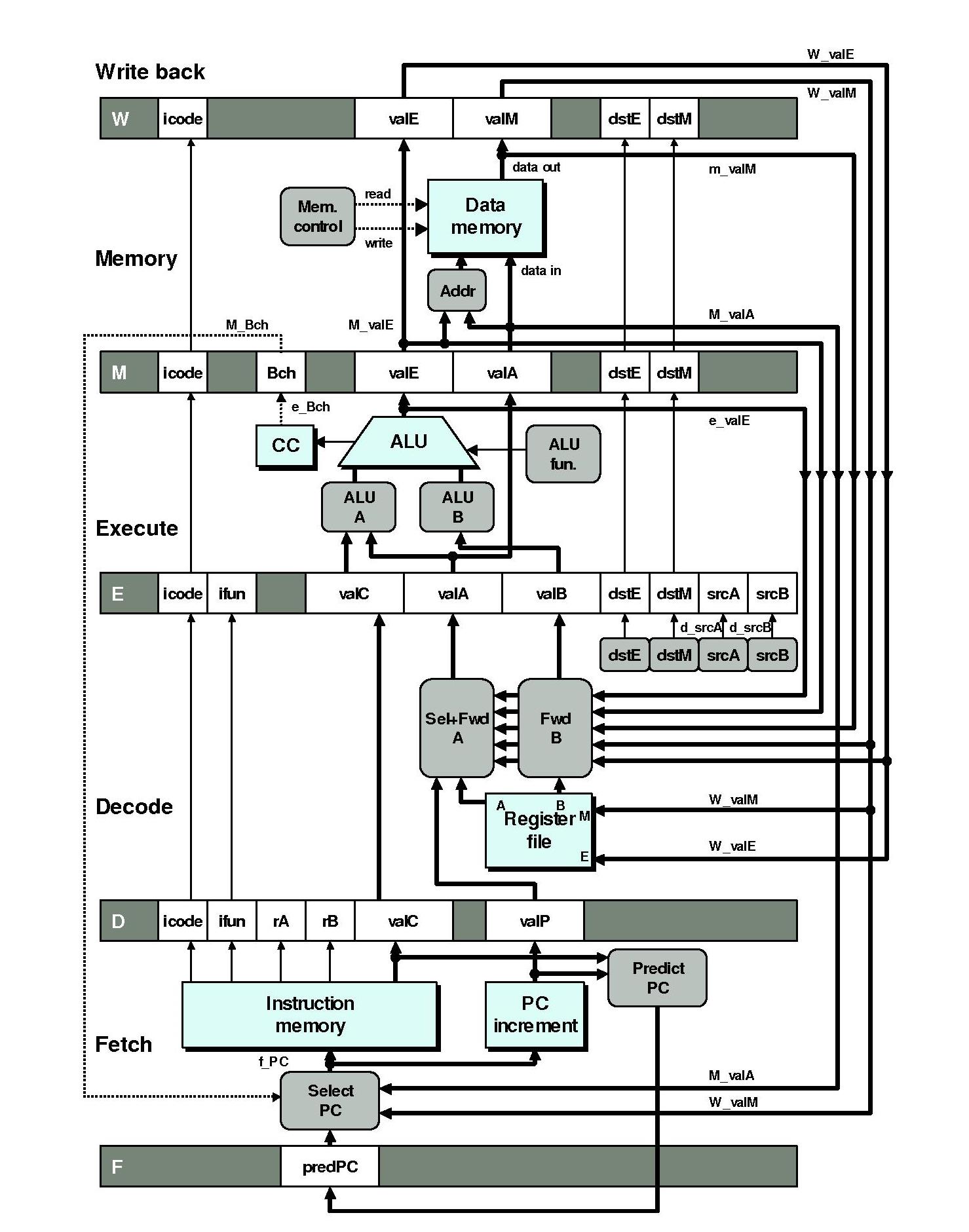

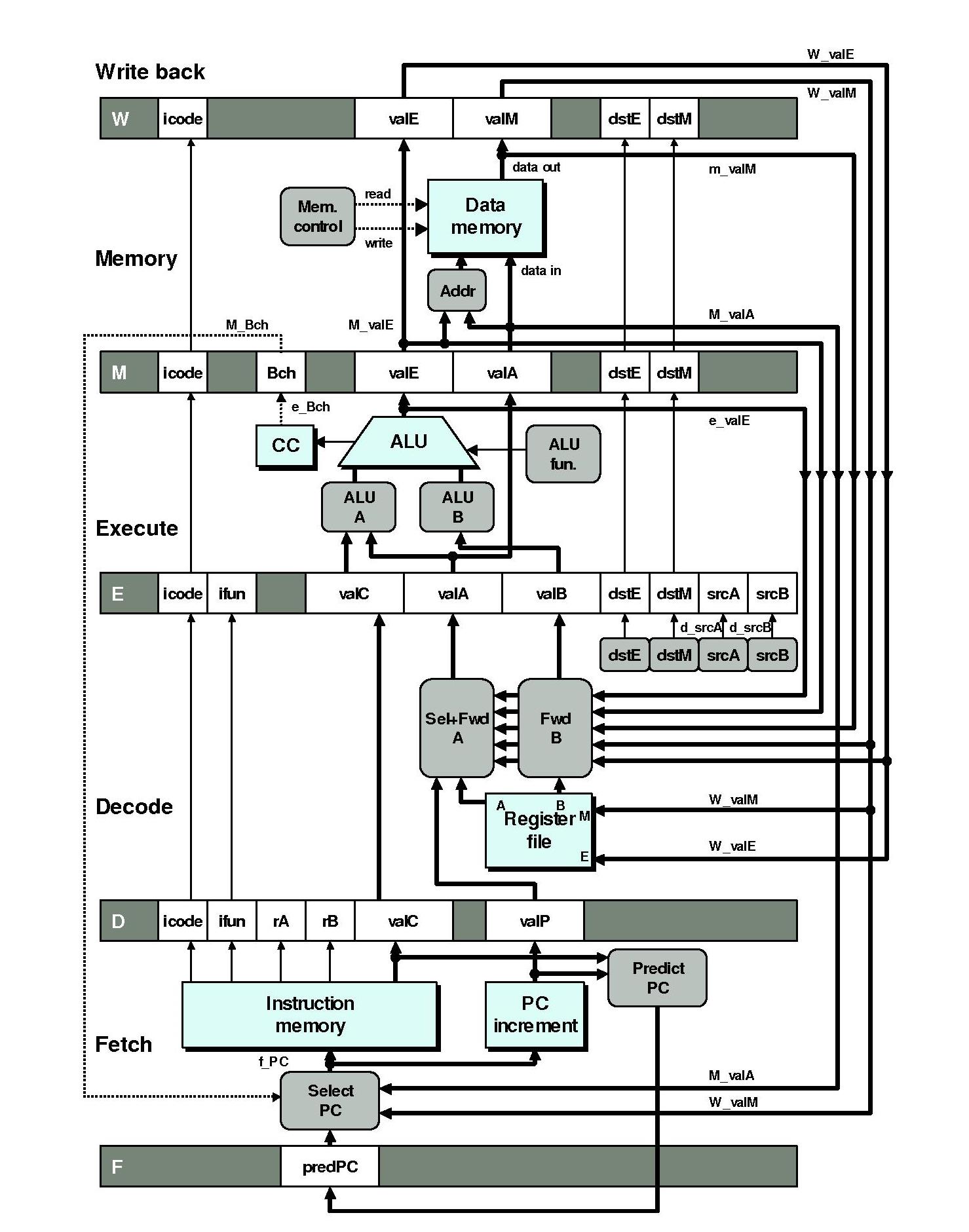

Structure générale

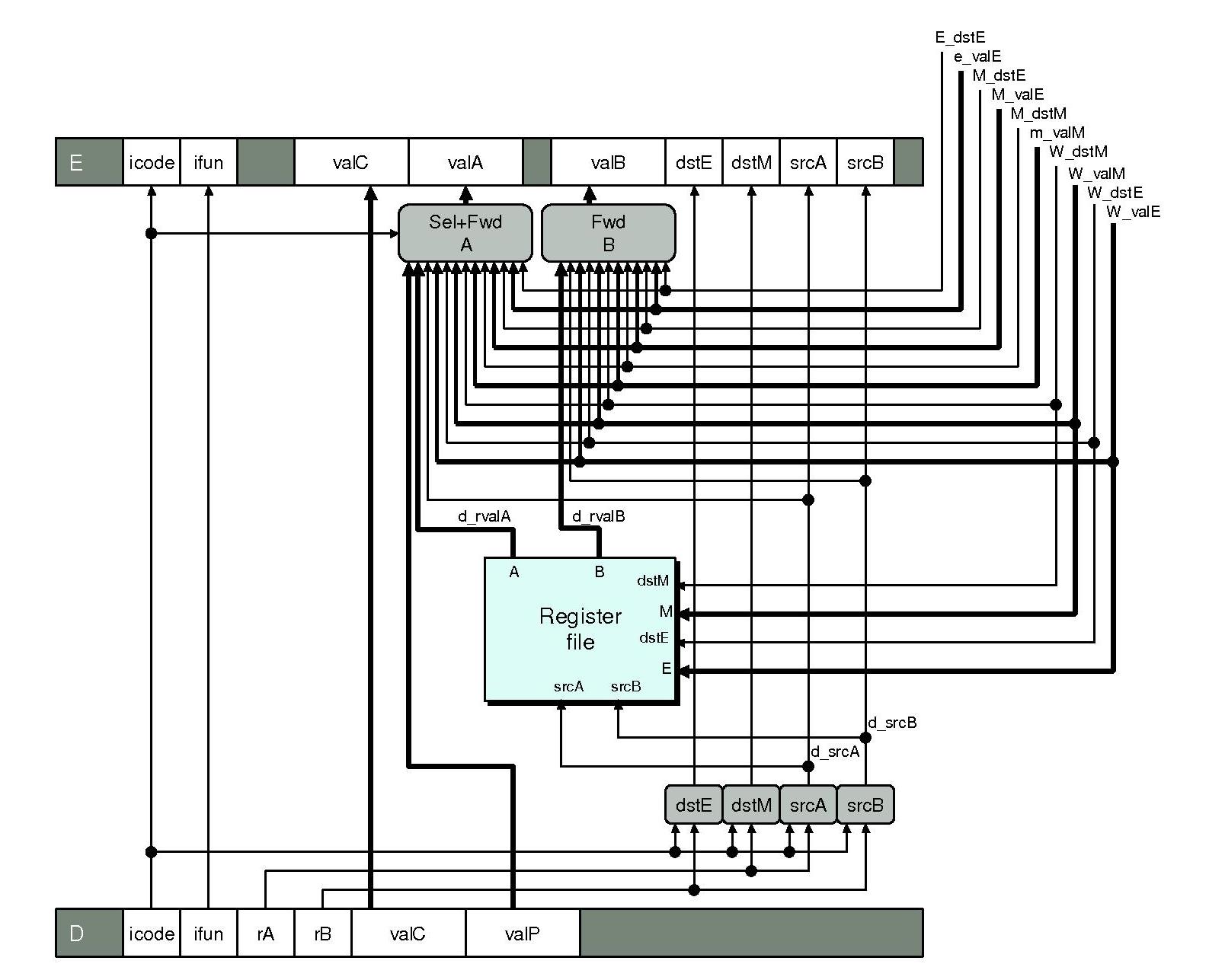

Conventions de notation

- new_E_valA : valeur valA qui sera enregistrée dans le registre E au prochain top d'horloge (et donc calculé par l'étage Decode).

- E_valA : valeur valA actuellement enregistrée dans le registre E (et donc disponible pour l'étage Execute).

- e_valE : valeur valE calculée par l'étage Execute.

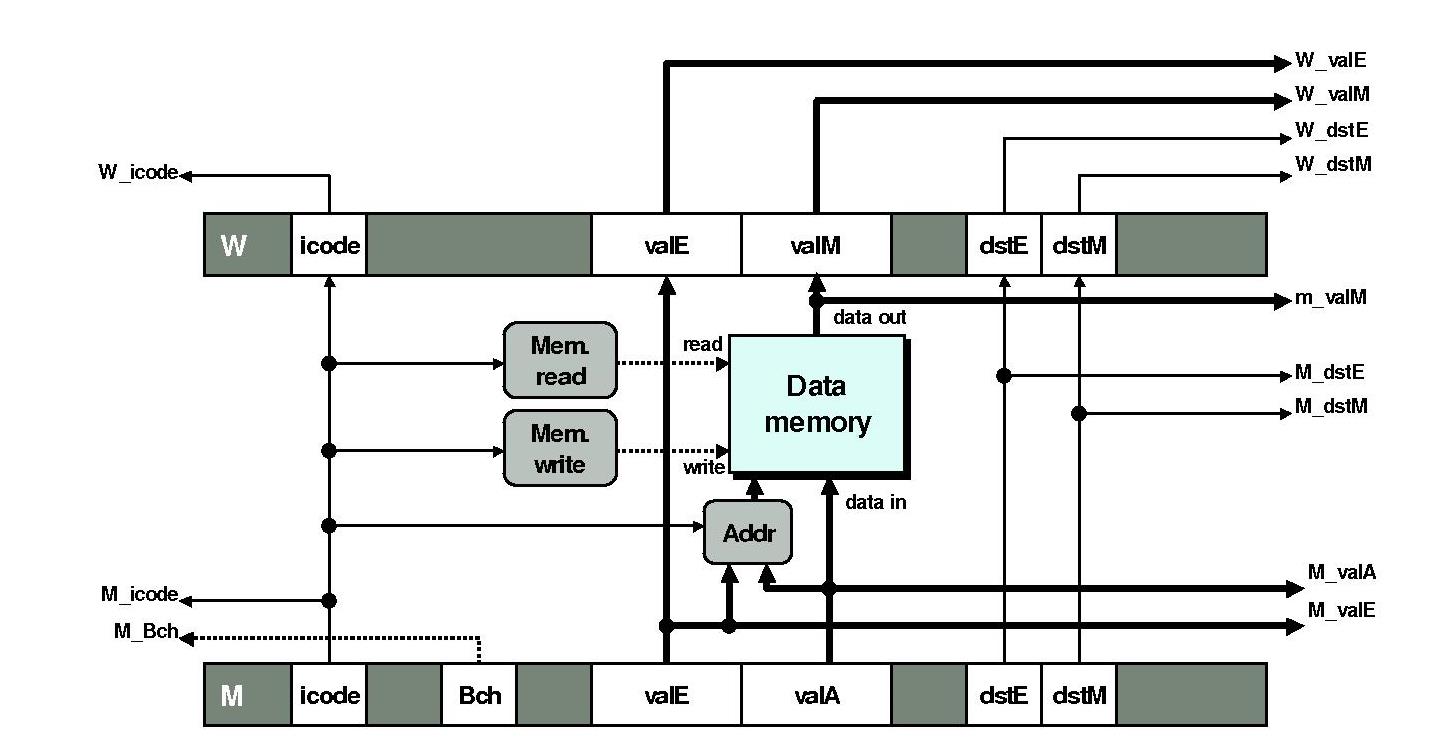

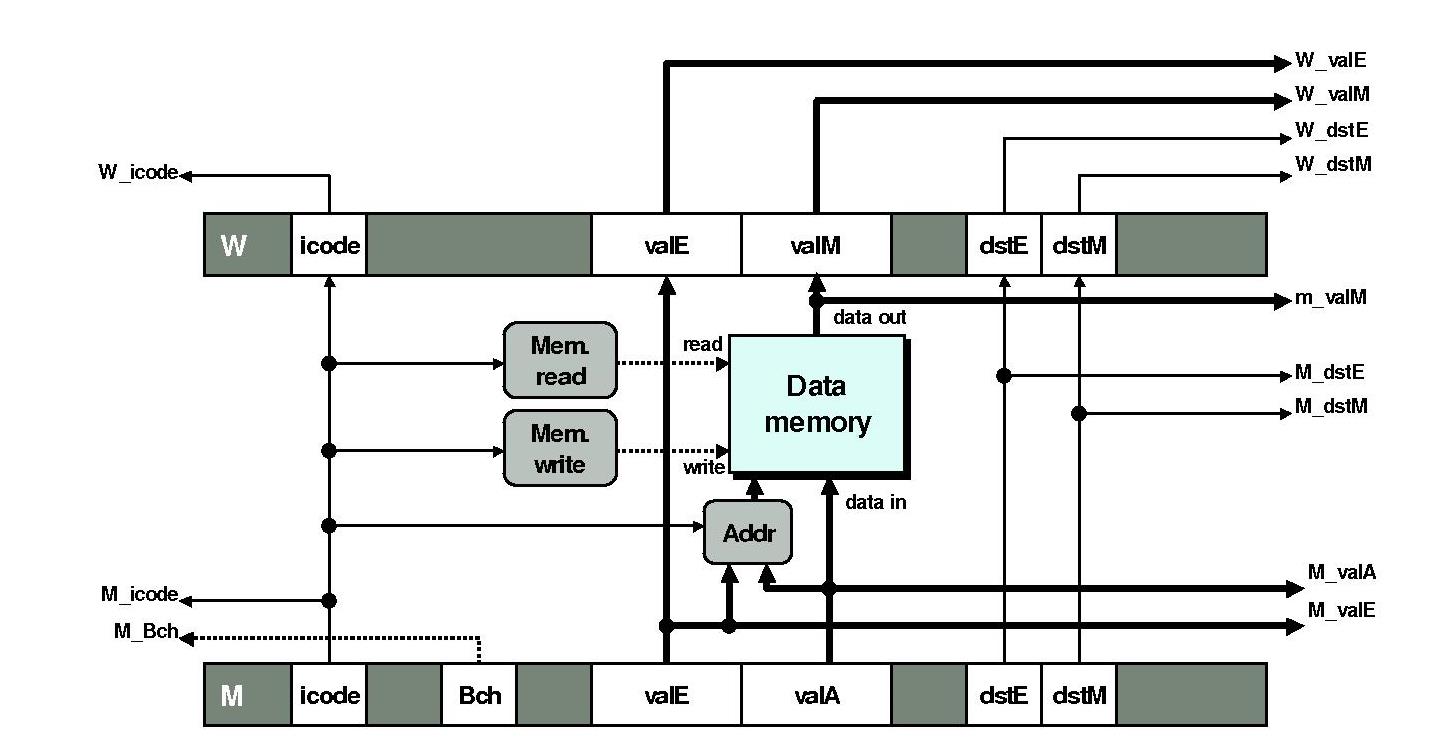

Étage Memory

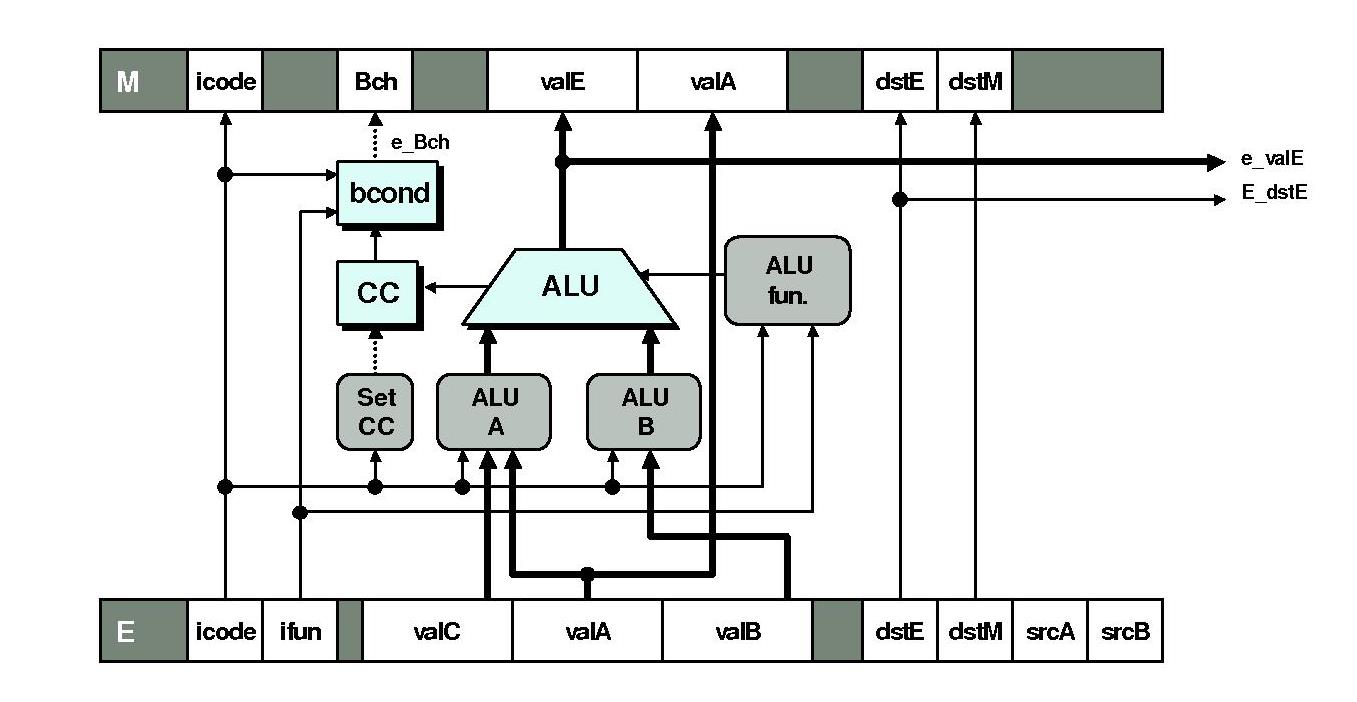

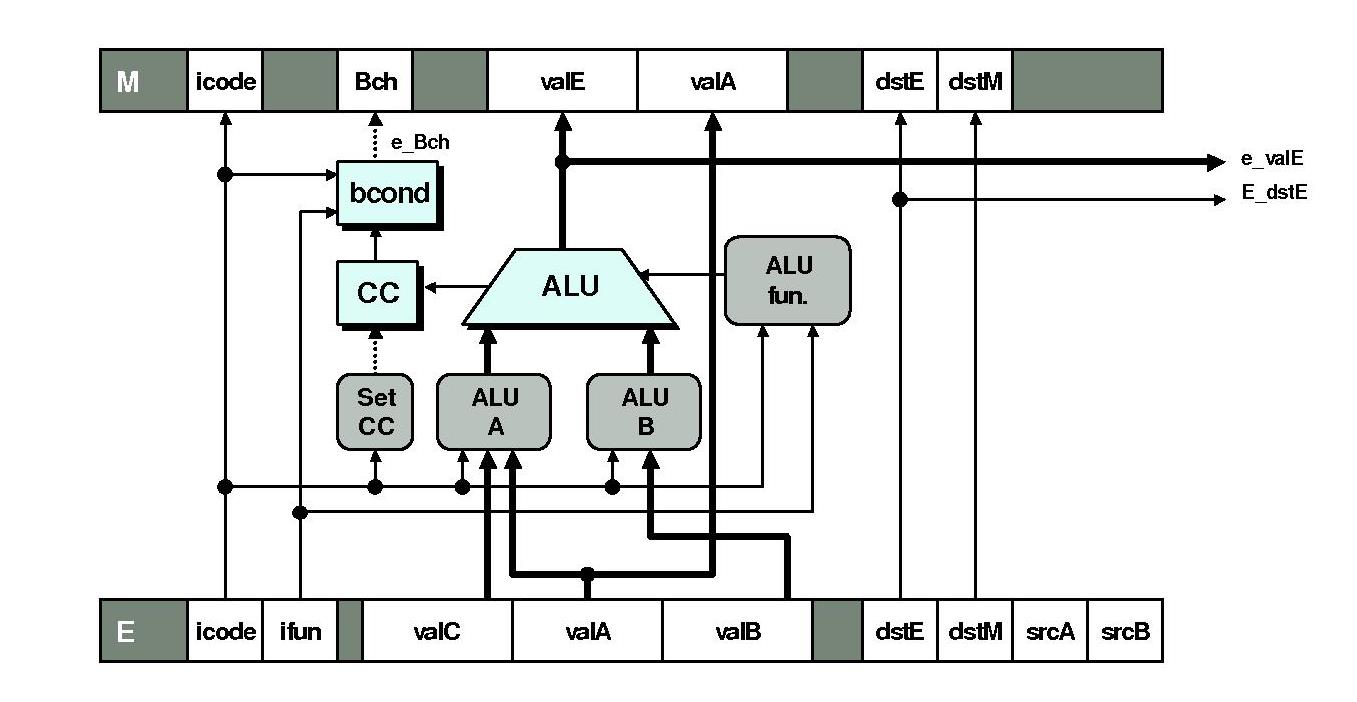

Étage Execute

# Should I stall or inject a bubble into Pipeline Register E?

# At most one of these can be true.

bool E_stall = 0;

bool E_bubble =

# Mispredicted branch

(E_icode == JXX && !e_Bch) ||

# Conditions for a load/use hazard

E_dstM in { d_srcA, d_srcB};

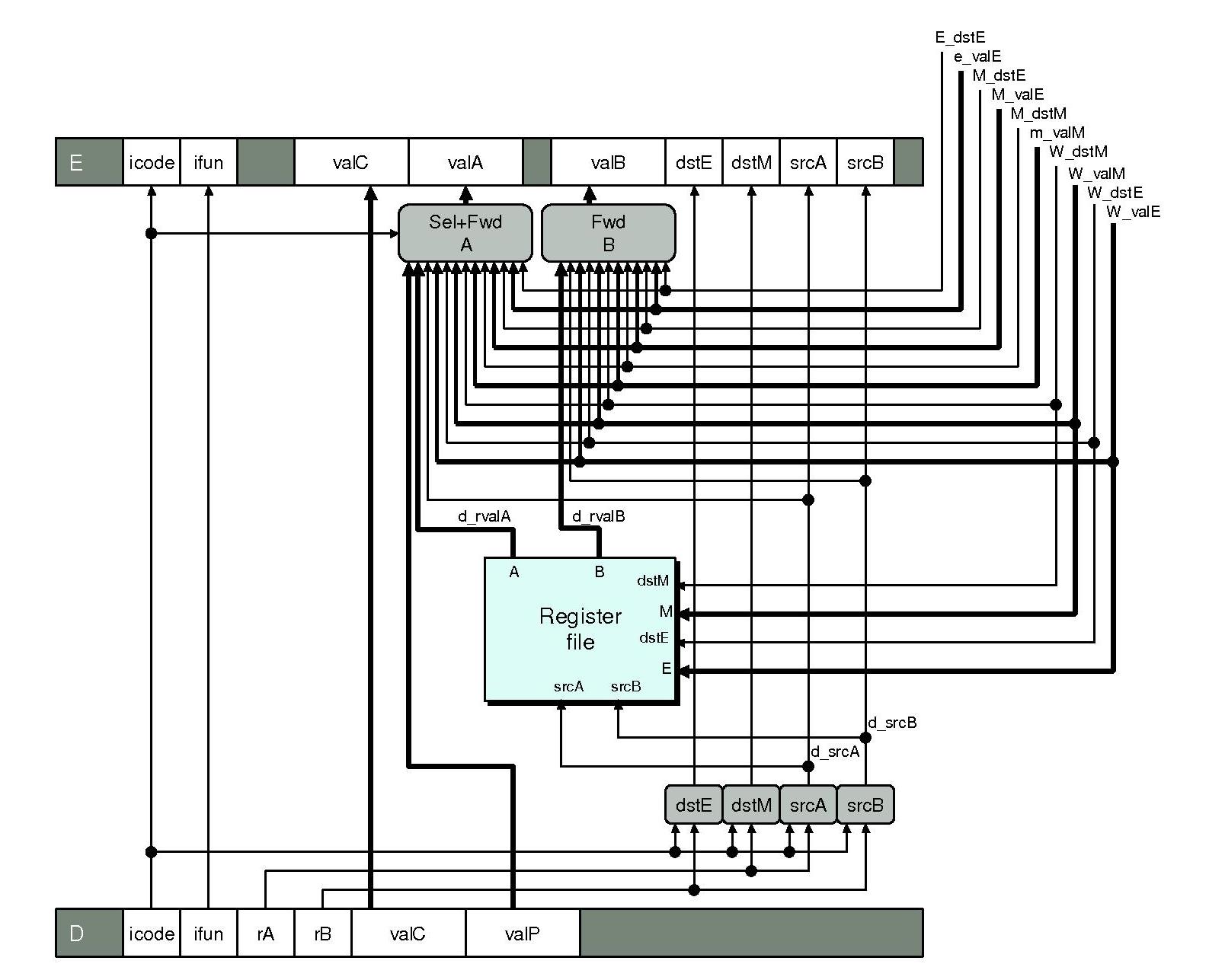

Étage Decode

int new_E_valA = [

D_icode in { CALL, JXX } : D_valP; # Use incremented PC

d_srcA == E_dstE : e_valE; # Forward valE from execute

d_srcA == M_dstM : m_valM; # Forward valM from memory

d_srcA == M_dstE : M_valE; # Forward valE from memory

d_srcA == W_dstM : W_valM; # Forward valM from write back

d_srcA == W_dstE : W_valE; # Forward valE from write back

1 : d_rvalA; # Use value read from register file

];

int new_E_valB = [

d_srcB == E_dstE : e_valE; # Forward valE from execute

d_srcB == M_dstM : m_valM; # Forward valM from memory

d_srcB == M_dstE : M_valE; # Forward valE from memory

d_srcB == W_dstM : W_valM; # Forward valM from write back

d_srcB == W_dstE : W_valE; # Forward valE from write back

1 : d_rvalB; # Use value read from register file

];

# Should I stall or inject a bubble into Pipeline Register D?

# At most one of these can be true.

bool D_stall =

# Conditions for a load/use hazard

E_dstM in { d_srcA, d_srcB };

bool D_bubble =

# Mispredicted branch

(E_icode == JXX && !e_Bch) ||

# Stalling at fetch while ret passes through pipeline

# but not condition for a load/use hazard

! E_dstM in { d_srcA, d_srcB } && RET in { D_icode, E_icode, M_icode };

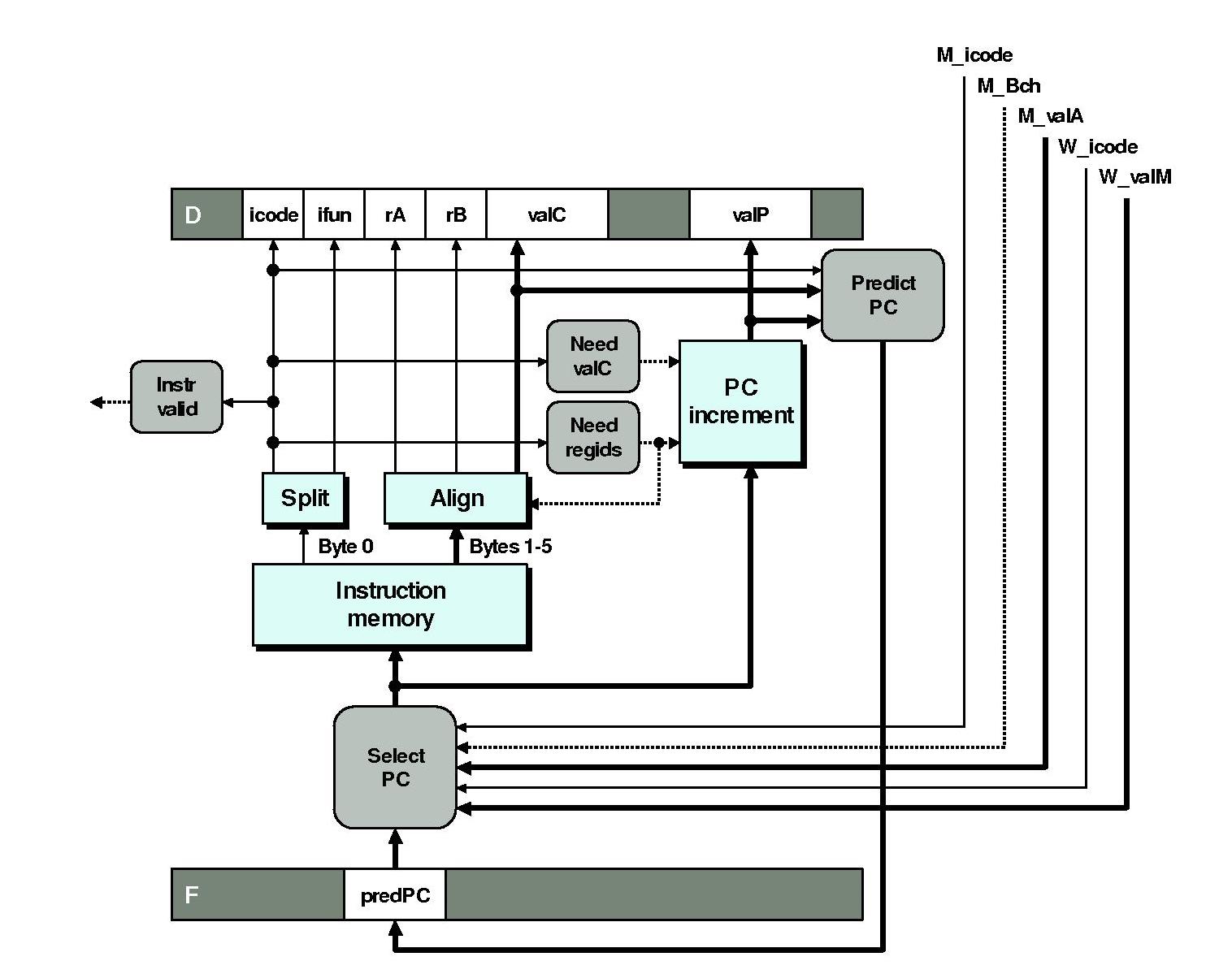

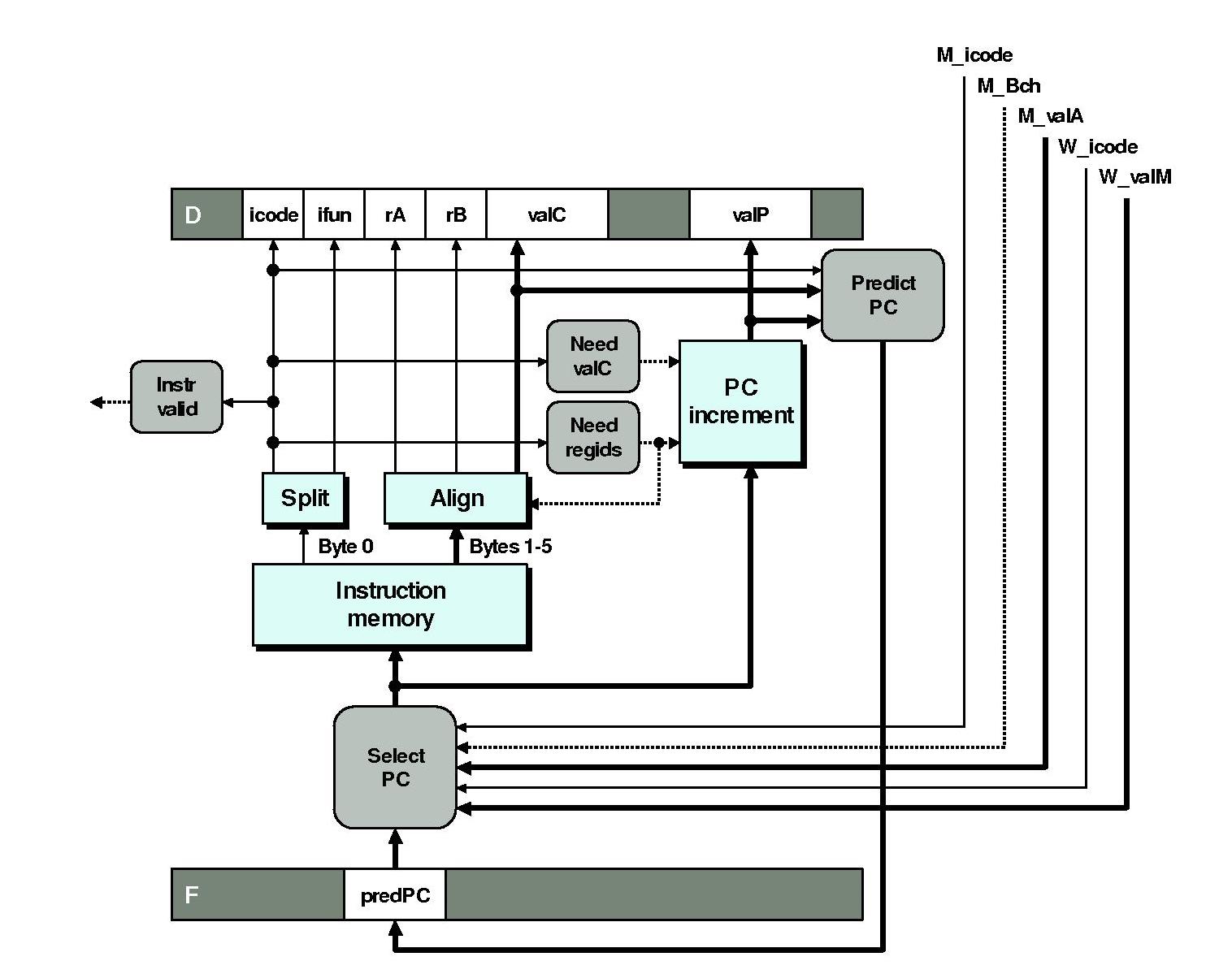

Étage Fetch

## What address should instruction be fetched at

int f_pc = [

# Mispredicted branch. Fetch at incremented PC

M_icode == JXX && !M_Bch : M_valA;

# Completion of RET instruction.

W_icode == RET : W_valM;

# Default: Use predicted value of PC

1 : F_predPC;

];

# Predict next value of PC

int new_F_predPC = [

f_icode in { JXX, CALL } : f_valC;

1 : f_valP;

];

# Should I stall or inject a bubble into Pipeline Register F?

# At most one of these can be true.

bool F_bubble = 0;

bool F_stall =

# Conditions for a load/use hazard

E_dstM in { d_srcA, d_srcB } ||

# Stalling at fetch while ret passes through pipeline

RET in { D_icode, E_icode, M_icode };